為滿足深亞微米(DSM)系統級芯片(SoC)設計的性能和可靠性要求,設計良好的電源分配網絡十分重要。隨著器件密度和時鐘頻率的增加,電源線和地線網絡傳送的交換電流也同樣增加,進而導致功率密度的增加,由于在DSM設計中采用的低電源電壓以及更細的線路,功率密度的增加將對電源網絡(Power Grid)的魯棒性產生不利影響。由于瞬間的高電流和電源線路的阻抗引起的器件電壓的大幅度下降,電源網絡更易受電壓降的影響,這就是通常所說的IR壓降現象。

由于大量持續不變的電流引起的電遷移效應,電源線路更容易失效,也易與附近的線路形成短路。IR壓降不僅影響電源網絡的完整性,而且延長了時序收斂的時間。門電路的供電電壓降低百分之五可以使門電路的延遲增加百分之十五。這些DSM效應使得電源網絡驗證已成為一個必不可少的設計過程,以確保新設計達到目標設計速度、滿足可靠性要求并且具備可制造性。

電源設計面臨的關鍵問題

電源網絡驗證的一個關鍵問題在于,到目前為止,都是在版圖設計完成之后才在設計流程中利用商用電源網絡驗證工具進行電源網絡設計。在設計后期,電源線路的互連寄生參數以及器件的電流消耗的大部分詳細數據已經完成,因而如果此時校正經驗證過的任何一處電源網絡問題,大量返工的代價非常昂貴。

TI公司已經為綜合了門級和晶體管級分析的SoC設計開發了一種新的分層式電源網絡驗證方法。該多級分層式驗證方法能夠提取電流在SoC芯片中的流動和分布情況,以便在物理設計周期或早在底層規劃階段發現潛在的電源網絡問題。例如TI的TMS320C6211 DSP芯片設計就是采用了這種新方法。

要利用新的電源網絡驗證方法,首先必須定義設計要求。SoC在單個芯片上集成了多級邏輯和功能,也就是說,單片電路上集成了扁平(Flat)門級綜合邏輯、分層門級模塊(如數據路徑)、晶體管級嵌入式IP模塊(如微處理器內核或存儲器)以及模擬電路等,因此,SoC驗證方法必須具備分層式的結構,并包括門級和晶體管級驗證。

在設計早期進行門級分析,有利于設計頂層電源網絡,并有利于針對未安置模塊規定電源網絡要求。

然而,僅依靠門級分析對電源網絡驗證PGS(Power Grid sign-off)來說不夠精確,因此,該方法必須包括電源網絡驗證,它在晶體管級對單元或者IP模塊的內部電源網絡進行建模,以便獲得精確的電流分配情況。

設計復用是SoC設計的核心,新方法要易于實現單元、模塊以及IP的復用。當一個單元或者IP模塊分析完成后,分析結果必須具備可復用性,因而避免為每個實例重新提取和重新分析該單元或IP模塊,分析結果的可復用性將對整個芯片電源網絡驗證的周期影響很大。我們選擇Simplex Solutions公司的Voltage Storm(VS)SoC設計工具,該工具能滿足TI對多級和分層式方法的所有要求。

電源網絡驗證新方法

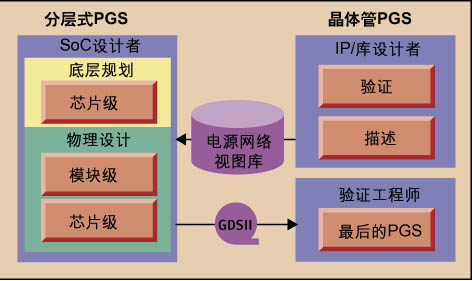

TI采用Simplex工具進行開發的方法如圖1所示。首先,庫設計小組對包括IP內核、存儲器和標準單元在內的所有葉片級(leaf-level)組件進行特征參數提取和驗證。這些電源網絡特征參數由GDSII版圖文件在晶體管級生成,以便精確地對電流分配建模。根據這些特征參數,庫設計人員能夠創建在驗證過程中使用的各種電源網絡視圖,包括底層規劃(或者模板)視圖、端口(或黑盒)視圖以及詳細的(或晶體管級)視圖。

底層規劃視圖由以下一些信息得出,包括:單元或者模塊端口的LEF描述;單元的高度、寬度、間距信息;用于電源布線的每個金屬層的方位等。

端口視圖是一個不帶晶體管的黑盒視圖,由某個單元庫的LEF描述來創建。它在該模塊的外圍端口還配有電流源,把電流均勻地分配到各端口。這個模型用于對底層規劃階段的標準單元建模,但不足以應付更復雜的IP模塊和PGS的應用設計要求。

IP模塊和標準單元的詳細電源網絡視圖由端口的LEF描述和版圖的GDSII描述來創建。詳細的視圖組件包括來自LEF的端口幾何形狀、來自GDSII的內部電源網絡以及來源于GDSII版圖的晶體管抽頭點的電流源。具體視圖包含晶體管級的詳細信息,可精確地模擬復雜IP模塊內部的電流分配和功耗情況。

在設計流程的下一步,芯片集成或物理設計小組利用布線的DEF描述及由庫設計小組創建的電源網絡視圖庫對底層規劃進行分析,模塊設計人員可以使用類似的方法分析他們設計的模塊。

如果DEF與用于輸出的GDSII版圖文件一致,那么對于大多數ASIC流程而言,一旦所有單元和IP模塊已經跟電源布線放置在一起,則進行的PGS。在這個設計階段,根據已經確定的電源網絡的完整性數據,設計人員可避免為電源網絡留出過多的空間,并使信號布線面積。

驗證新的設計方法

如果在布局布線之后,設計小組又對的設計進行了重要的修改,那么物理驗證小組負責進行版圖與原理圖驗證,并檢查設計規則,同時在晶體管級執行PGS以及在的GDSII版圖上進行一次扁平分析(flat analysis)。

用于驗證新方法的芯片是TMS320C6211,是帶有一個兩級高速緩存結構的定點VLIW數字信號處理器。C6211采用五層金屬工藝,包含600萬個晶體管,在這個DEF中有大約1.16萬個布線網絡,放置了2.29萬個對象,標稱工作電壓是1.8V。

步:生成電源網絡視圖。

首先,要創建TMS320C6211各種組件的電源網絡視圖庫。C6211包含一個C62xVLIW DSP內核和17個嵌入式SRAM。在DSP內核和嵌入式SRAM中,由于電流分布的非均勻,很有必要利用VS SoC工具創建的詳細電源網絡視圖的晶體管級建模。TI的開發人員也創建了若干組件的底層規劃視圖,以便在底層規劃過程中使用。

第二步:在底層規劃過程中進行分析。

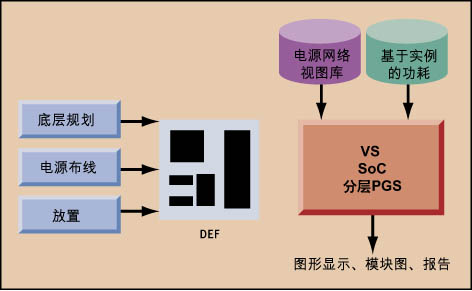

在底層規劃過程的早期,模塊的其余部分還未創建,所以能夠修改DSP內核的版圖。用于全芯片分析的VS SoC輸入包括:全局電源布線的芯片級DEF、基于實例的功耗數據、DSP內核的詳細晶體管級視圖以及其它模塊的底層規劃視圖(圖2)。該分析的執行發生在全局電源布線和布局之后、信號線布線之前,使人們能看到通過DSP內核的電流及其對附近邏輯電路的影響。在400MHz的SUN Ultrasparc-II工作站上,該分析僅需要運行六分鐘并占用60MB存儲器。

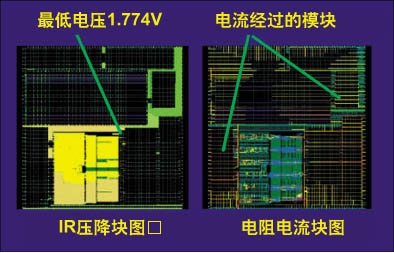

分析表明,電源布線太保守,其實增加IR壓降的容限仍然可以達到設計要求。在VS SoC中使用PGS探測特性來檢查改變電源布線的DEF的影響。利用“Scaling”特性,可以在高IR壓降區域增加走線和過孔,在低IR壓降區域刪除走線和過孔。電壓從1.774V下降到1.770V,仍在規定范圍之內,從而節省了寶貴的布線資源。

第三步:電源網絡驗證

在完成全局電源布線、單元放置和信號線布線之后,接著就進行全芯片分層式電源網絡IR壓降驗證。用于該分析的VS SoC輸入包括信號和電源布線的芯片級DEF、基于實例的功耗以及DSP內核、SRAM和標準單元的詳細視圖。

為了對每個模塊進行精確的功耗估計,TI使用Synopsys公司的晶體管級仿真工具Powermill。對于版圖設計前分析,要創建Powermil所需的SPICE模型架構(deck),該SPICE模型架構則通過Synopsys包含對線電容的線負載模型估值的已綜合數據庫得到。對于版圖設計后分析,開發人員根據版圖設計后EDIF網表創建Powermill所需的SPICE模型架構,該EDIF網表包含用Simplex的Fire&Ice QX提取的后端注釋寄生電容。

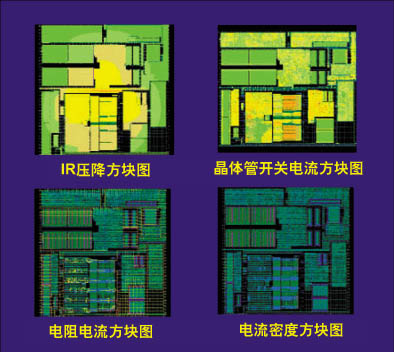

在定型的DEF上用VS SoC進行全芯片分層式分析, 400MHz的SUN Ultrasparc-II工作站需要運行22分鐘并占用550MB存儲器。除了IR壓降分析,全芯片分析還產生了其他一些電源網絡信息,包括電阻電流、抽頭電流(tap current)和電流密度方塊圖。圖4的方塊圖將電源網絡的行為形象地表現出來,例如,抽頭電流的分配表明存儲器中電流非常低,DSP內核中的電流較高,正如預期那樣。

驗證精度

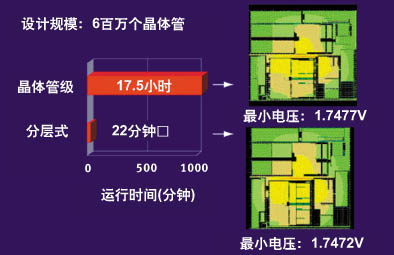

利用VS SoC的DEF分析速度很快,與現有的版圖設計后晶體管級電源網絡提取和分析所用的17.5個CPU小時相比,它只需要22個CPU分鐘,但是,分析精度也很重要。為了驗證分層式分析的精度,開發人員利用現有的電源網絡驗證方法,在定型的GDSII版圖上對該電源網絡進行了一項扁平的、晶體管級的分析。

根據該分析計算出的小工作電壓為1.7477V,IR壓降為0.0523V;而根據分層式分析計算出的小工作電壓為1.7472V,IR壓降為0.0528V,幾乎與晶體管級分析的結果相同,誤差在0.1%以內。

Simplex將精度的提高歸因于Accura靜態分析專有技術,它能分析時鐘域、識別存儲器和門電路,并根據基本輸入分析傳輸行為。

對時序的影響

非均勻電源分配會影響芯片性能,因此必須對其進行DSM SoC時序驗證。在討論時序收斂環路時,IR壓降對時序的影響已被忽略,這是因為很難獲得IR壓降對時序影響的數據,也很難獲得扁平晶體管級分析的長期循環時間數據。試驗表明,將VS SoC分層式分析得到的基于實例的IR壓降數據加入到延遲計算器(Synopsys的Primetime),可以獲得IR壓降對時序的影響。

開發人員用手工方法將基于實例的IR壓降數據加入Primetime工具,并建立了用于不同級別的IR壓降(2%、5%、10%)的多個Synopsys單元庫,然后,根據VS SoC得到的IR壓降數據為Primetime分析選擇庫單元。

本文結論

電源網絡驗證SoC設計方法的一個重要組成部分。利用VS SOC能夠開發一種新型用于包含門級和晶體管級分析的電源網絡驗證的分層式方法。TI的開發人員現在能夠使其設計中的電流表現可視化,并且在物理設計早期驗證其電源網絡設計的完整性。早期分析使設計者容易實現對電源網絡的修改且成本。

電源網絡驗證也避免了不必要且普遍存在的電源網絡設計冗余度太大的問題,并且還能顯示時序驗證流程中的IR壓降等數據。